Glitch free clock muxing is tricky. Some designers take it on the safe side and disable both clocks, do the switch and enable the clocks back on. Actually, I do not intend to discuss all the details of glitch-free clock muxing, a nice and very readable article can be found here.

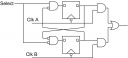

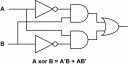

If you finished reading the article above and are back with me, I want you to take a closer look at the second implementation mentioned. Here is a copy of the circuit for your convenience

The key question addressed by the author of the article is what happens if the select signal violates setup and hold conditions on one of the flip-flops? Apparently the flip-flop would go meta-stable and a glitch might occur, right? After all why was the synchronizer introduced in the 3rd circuit on the article. Well take a closer look!!

On closer look we see that both flip-flops operate on the falling edge of the clock, this means that a meta-stable state can occur when the clock is transitioning from a high to a low. But, since after the transition the clock is low, the AND gate immediately after the flop will block the unstable flop value for the entire low period of the clock. Or in other words the meta-stability has the entire low period of the clock to resolve and will not propagate through during this time. Isn’t that absolutely cool??!!

I have to admit that upon seeing this circuit for the first time I missed this point, only after reading one of the application notes at Xilinx it dawned on me. The link can be found here (item #6)